UVVM یکی از سریعترین روشهای تأیید در صنعت EDA است که در سال 2015 راه اندازی شد و توسط حدود 20٪ از تمام طراحان VHDL FPGA مورد استفاده قرار گرفت.

امروز ، تأیید طراحی بیش از نیمی از زمان کلی پروژه را تشکیل می دهد. روش های تأیید برای تخفیف این گلوگاه وجود دارد ، جایی که یک روش معمولاً شامل یک ترتیب سنج (وسیله ای برای ارسال داده ها و کنترل دستگاه تحت آزمایش [DUT]) ، مدل ها (بیان کننده نحوه رفتار اجزا) و یک جدول امتیاز (وسیله ای برای مقایسه) است. رفتار DUT در برابر مدل).

برخی از راه حل ها برای دهه ها وجود داشته است. به عنوان مثال ، روش جهانی تأیید (UVM) ریشه در زبانی دارد که برای تأیید در سال 2001 ساخته شده است. با این حال ، UVM بر اساس زبان SystemVerilog است در حالی که حدود نیمی از کدهای جامعه طراحی FPGA در VHDL. برای آنها ، روش تأیید مبتنی بر VHDL سریعتر و کارآمدتر است.

هنگامی که رایگان / منبع باز باشد ، حتی خبر بهتری است.

به عنوان مثال ، روش تأیید منبع آزاد VHDL (OS-VVM) که در سال 2012 راه اندازی شد ، در سال 2018 به عنوان کتابخانه تأیید شماره 1 نامگذاری شد و همچنان بسیار محبوب است. همچنین ، جیم لوئیس ، مدیر ارشد آن ، از Synthworks ، با گروه استاندارد IEEE VHDL همکاری نزدیک دارد.

یکی دیگر از موارد اضافه شده در صنعت ، روش جهانی تأیید VHDL (UVVM) است. این در سال 2015 راه اندازی شد و طرفداران فزاینده ای دارد.

بنابراین ، نمره چیست؟

UVVM یک روش و کتابخانه رایگان است (برای بارگیری از سایت www.github.com/uvvm) برای ساخت میزهای آزمایشی مبتنی بر VHDL. این شامل عناصر زیر است: یک کتابخانه ابزار ، یک چارچوب م componentلفه تأیید VHDL (VVC) و مدل های عملکردی گذرگاه (BFM).

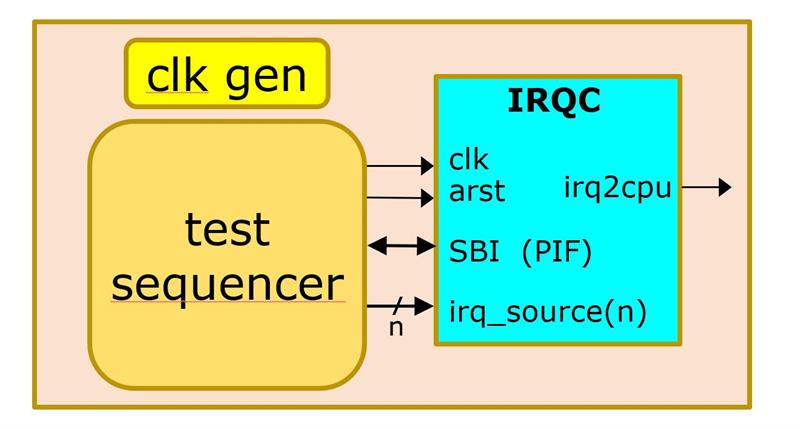

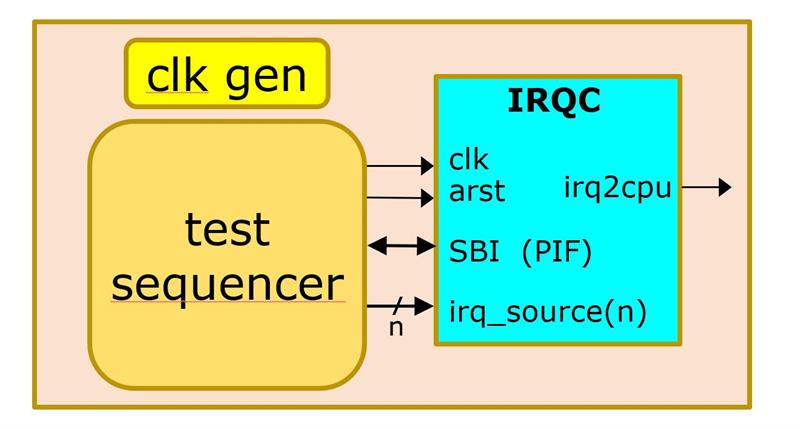

برای نشان دادن این موارد ، بهتر است یک سناریو راستی آزمایی را در نظر بگیرید. شکل 1 نیمکت آزمون را برای یک کنترل کننده وقفه ساده (IRQC) نشان می دهد.

این نیمکت آزمون شامل DUT (یعنی IRQC) است که دارای یک ساعت (clk) ، یک تنظیم مجدد (arst) ، یک رابط باس ساده (SBI) ، تعدادی (n) از منابع وقفه (irq_source (n)) و وقفه در نتیجه پردازنده (irq2cpu). نیمکت تست دارای یک مولد ساعت و یک ترتیب سنج آزمایش است.

در بالا: میز آزمایش IRQC

در UVVM ما با ایجاد یک روش همزمان مولد ساعت را ایجاد می کنیم:

ژنراتور_ ساعت (clk ، GC_CLK_PERIOD).

سپس یک ترتیب سنج آزمایش برای کنترل شبیه سازی ایجاد می کنیم. اولین کاری که باید انجام دهد ارسال پیام است تا به ما اطلاع دهد که شروع شده و منتظر چیزی نیست. در کد ، ممکن است داشته باشیم:

ورود به سیستم (ID_LOG_HDR ، "شبیه سازی IRQC_TB شروع شده").

در مرحله بعدی ، باید بررسی کنیم که وقفه در پردازنده در حال حاضر منطق صفر است ، اگر این یک خطا نیست. کد این ممکن است:

check_value (irq2cpu ، "0" ، "irq2cpu پیش فرض غیرفعال").

سپس باید ثبات سیگنال را بررسی کنیم ، زیرا نمی خواهیم وقفه در CPU افزایش یابد. باید از 0 ثابت به 1 ثابت برسد:

check_stable (irq2cpu ، اکنون - v_reset_time).

در IRQC می خواهیم پالس تولید کنیم. اگر می خواهیم یک پالس بر روی منبع شماره 2 قرار دهیم ، کد زیر است:

gen_pulse (irqc_source (2) ، '1' ، clk_period ، "تنظیم منبع 2 برای دوره ساعت").

یکی دیگر از ویژگی های مهم نیمکت آزمون انتظار برای مقادیر است ، اما ما نمی خواهیم برای همیشه. به عنوان مثال ، اگر منبع وقفه را زیاد رانده ایم ، انتظار داریم كه خروجی IRQC بلافاصله فعال شود ، بنابراین بیایید منتظر بمانیم دو دوره زمانی 2:

await_value (irq2cpu، '1'، 0 ns، 2 * C_CLK_PERIOD، "وقفه فوراً انتظار می رود").

همچنین ، بیشتر نیمکت های آزمایشی به BFM نیز نیاز دارند. آنها برای دسترسی به رابط ها مورد نیاز هستند. بنابراین می توانیم یک مقدار (مثلاً AA) به آدرس رجیستر ماشه وقفه بنویسیم

sbi_write (C_ADDR_ITR ، x "AA" ، "ITR: تنظیم وقفه ها")

… و بررسی کنید که آیا می توانیم دوباره آن را بخوانیم read

sbi_check (C_ADDR_IRR ، x "AA" ، "IRR")

... اگر نمی توانیم یک خطا را گزارش دهیم

در UVVM می توان میزان خواندن را در برابر مقدار مورد انتظار بررسی و پیام های دارای مهر زمان را دریافت کرد. به عنوان مثال ، کد ترتیب سنج برای بررسی اینکه 00 سیگنالی به نام 'dout' باشد 00 است:

check_value (dout ، x "00" ، "dout باید به طور پیش فرض غیرفعال باشد")

اگر همه چیز خوب است ، گزارش پیام ممکن است گزارش دهد:

60 ns irqc_tb check_value (slv x00) => خوب. dout باید به طور پیش فرض غیرفعال باشد.

یا اگر خراب شود ، ممکن است موارد زیر را دریافت کنیم:

خطا:

192 تعداد irqc_tb

مقدار این بود: 'xFF'. انتظار می رود "x00".

dout باید به طور پیش فرض غیرفعال باشد

توابع log () ، check_value () ، await_value () فقط برخی از موارد موجود در کتابخانه ابزار UVVM است.

VVC ها

بیایید یک مثال BFM دیگر را در نظر بگیریم. ارتباطات داده این بار شکل 2 یک میز آزمایش برای UART را نشان می دهد.

میز تست دارای یک رابط گذرگاه ساده (SBI) ، RX و TX است که برای آن به سه BFM و یک ترتیب سنج آزمایش ، p_main نیاز داریم. برای استفاده از رابط های ماژول UART ، می توانیم به عنوان مثال استفاده کنیم:

sbi_write (C_TX ، x "B3")

… برای شروع انتقال اطلاعات سریال UART از طریق TX و به دنبال آن

uart_ Expect (x "B3")

… برای بررسی داده های منتقل شده بر روی خروجی سریال TX همانطور که توسط sbi_write () فوق آغاز شده است.

به طور مشابه ، ما می توانیم از uart_transmit () برای اعمال داده ها (به عنوان مثال x2A) در ورودی سریال UART RX و به دنبال آن sbi_check () استفاده کنیم تا تأیید کنیم

منبع: https://www.newelectronics.co.uk/electronics-technology/faster-fpga-verification/228138/